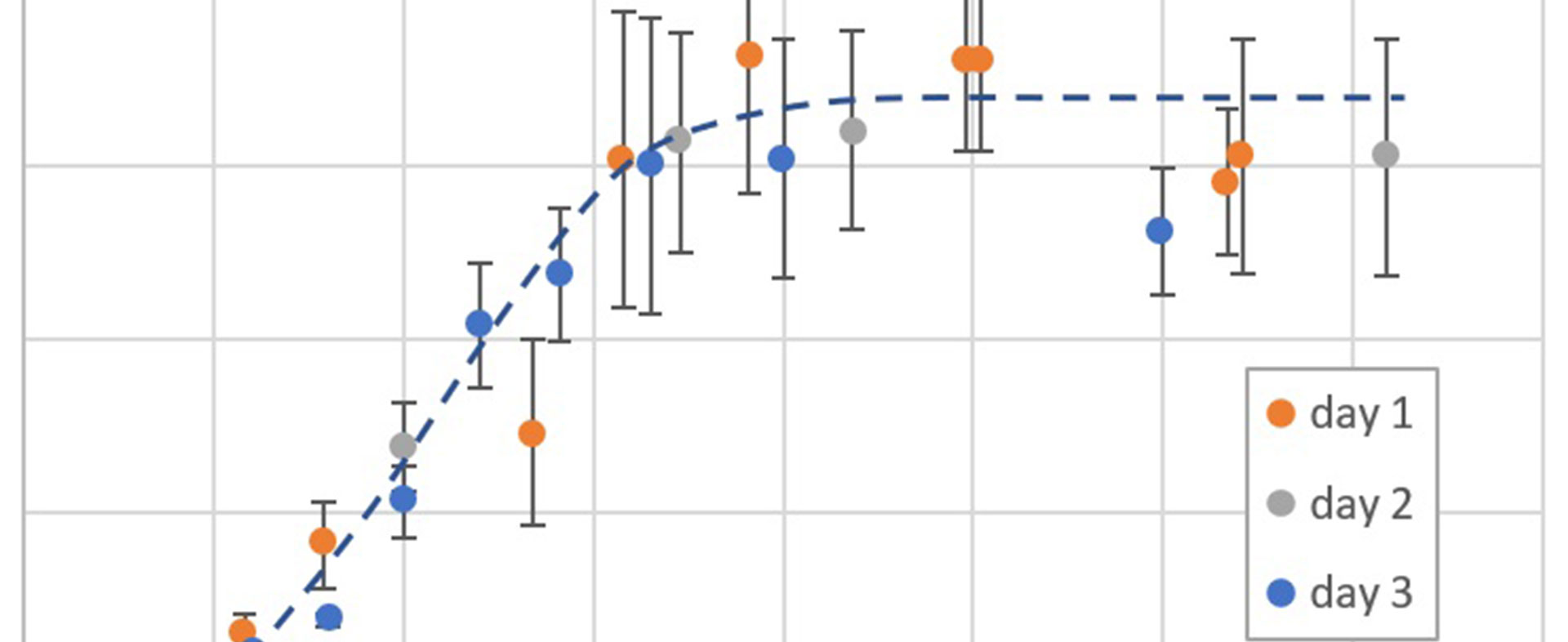

Dünne Silizium-Wafer lassen sich mit elektrostatischen Stützträgern herstellen – ohne negative Auswirkungen auf die elektrischen Eigenschaften der Halbleiterchips. Folge: eine verringerte Bruchrate.

Si-Chips, die dünner als 150 µm sind, können mit höheren Strömen betrieben werden. Sie lassen sich flächenoptimiert und damit energiesparend etwa in Transistormodulen oder in flachen und flexiblen Bauformen einsetzen. Um die Bruchraten dünner Si-Wafer zu reduzieren, aus denen die Chips hergestellt werden, sind elektrostatische Träger („EST-Träger“) eine einfache Lösung – sie halten die dünnen Si-Wafer bei kritischen Prozessen.

rechts: Prozesswafer auf EST-Träger vor dem Prozessieren in einem Hochtemperaturofen (Quelle: SEMIKRON Elektronik GmbH & Co. KG)

Das Ziel des Projektes war, EST-Träger mit geeigneten Elektrodendesigns herzustellen und den Herstellungsprozess dünner Si-Chips zu erproben.

Die EST-Träger wurden auf der Basis von Si-Wafern mit einem speziellen Design ausgeführt – Metallelektroden und Rückseitenkontaktierungen waren gegeneinander isoliert. Dabei war es eine besondere Herausforderung, Isolatormaterialien und Durchkontaktierungen zu entwickeln. Es konnten EST-Träger mit einer elektrostatischen Haltespannung bis 250 V hergestellt werden, die dünne Si-Wafer tagelang bei Raumtemperatur halten. Der „Waferstapel“ aus Dünnwafer und EST-Träger kann mit Standard-Equipment gehandhabt werden, etwa bei der Ionenimplantation und bei Metallisierungsprozessen. Folge: Die Bruchrate kann drastisch gesenkt werden. Für den Einsatz bei höheren Temperaturen (über 200°C) müssen die rückseitenkontaktierbaren EST-Träger allerdings noch besser isoliert werden.

Es konnte nachgewiesen werden, dass sich die elektrischen und mechanischen Eigenschaften der Leistungshalbleiterchips, die mit EST-Trägertechnologie hergestellt werden, nicht von herkömmlich erzeugten Bauelementen unterscheiden. So stellt die EST-Stützträgertechnologie eine zukunftsweisende Technik dar, mit der dünne Leistungshalbleiterbauelemente einfach, automatisiert und die Ausbeute steigernd gehandhabt werden können.