Je kleiner die Strukturen von Prozessoren werden, umso anfälliger zeigen sie sich für Rechenfehler. Um Prozessoren (CPU) und Speicher besser zu schützen, forschte das Verbundprojekt „Multi-Core Safe and Software-Intensive Systems Improvement Community“ (FORMUS3IC) an Verfahren der Fehlererkennung und -eliminierung.

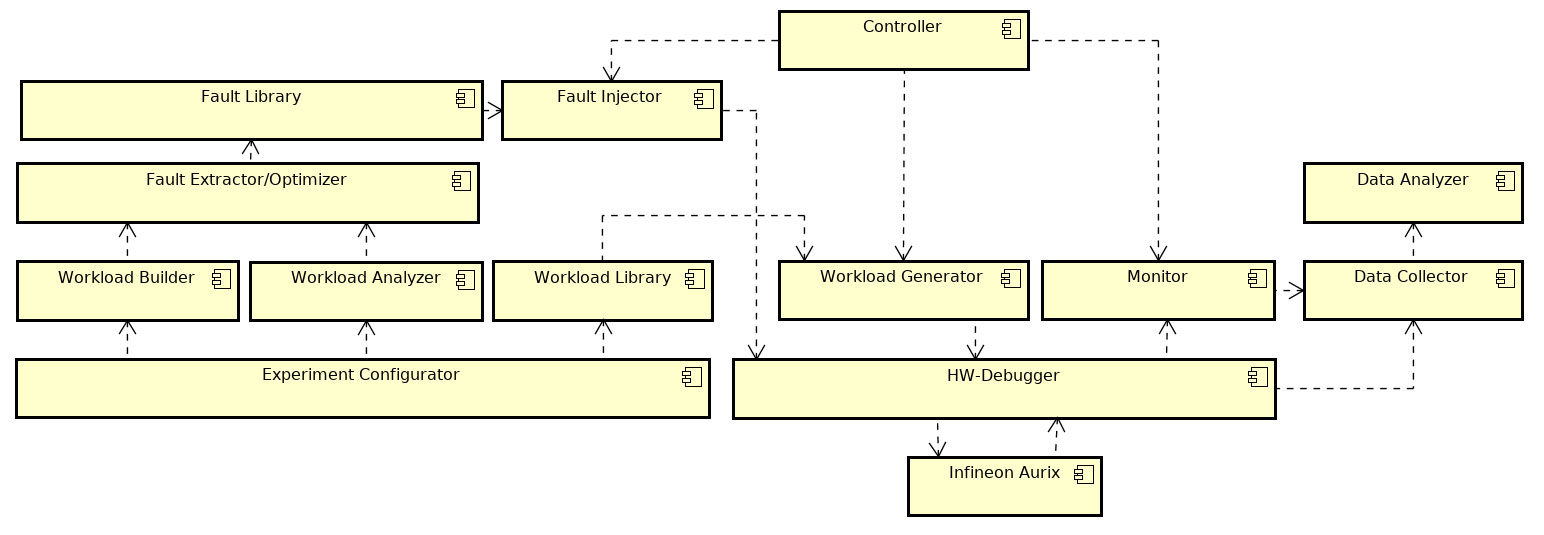

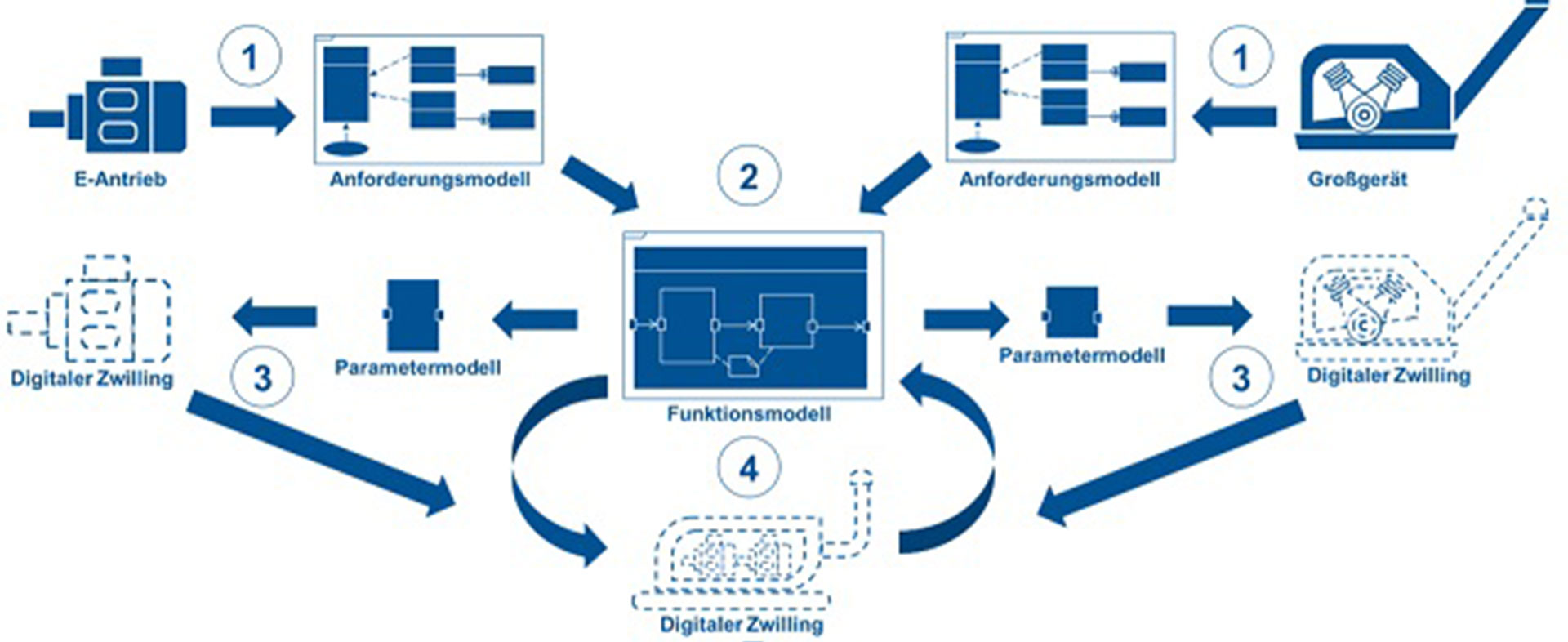

Die Forschungen sind ein Beitrag für die Nutzung sicherer, heterogener und paralleler Hardwareplattformen. Die Verfahren zur Systemsicherung umfassten die Architekturbeschreibung und die Time Simulation, die funktionale Sicherheit und die Verifikation, die Model-Verfeinerung und hardwarenahe Simulation mit Prozessormodellen, Parallelisierungstechniken und -pattern sowie Kommunikation. Der Nachweis technologischer Machbarkeit wurde durch drei Demonstratoren erbracht, Validierung mit eigener Fault-Injection-Plattform inklusive. Mittels Mehrheitsentscheid auf mehreren identischen Elementen konnten Fehler identifiziert und maskiert werden. Trotz erkannter Fehler lief das System weiter. Multicore-Plattformen beschleunigten das Verfahren. Das Resultat: ein Mehr an Sicherheit bei geringeren Kosten. Zudem verbesserte sich die Echtzeitfähigkeit. Mehrkerntechnologien lassen hardwarebasierte Ausfälle nicht sonderlich ins Gewicht fallen. Es bleiben stets Kerne zur Problembearbeitung übrig.

Das Lösungskonzept berücksichtigte die Bandbreite abstrakter Entwurfsmethodiken (formale Verifikation, Modellierung des Softwareentwurfs, Hardware-Virtualisierung). Das Projekt hatte das Ziel, Scheduling, Energieeffizienz und Sicherheit in Automotive und Avionik-Applikationen zu optimieren. FORMUS3IC leistete sowohl einen wissenschaftlichen als auch technischen Beitrag zur Anpassung des Entwicklungsprozesses an die neuen Herausforderungen durch Multi- und Manycore-Systeme.